Product Summary

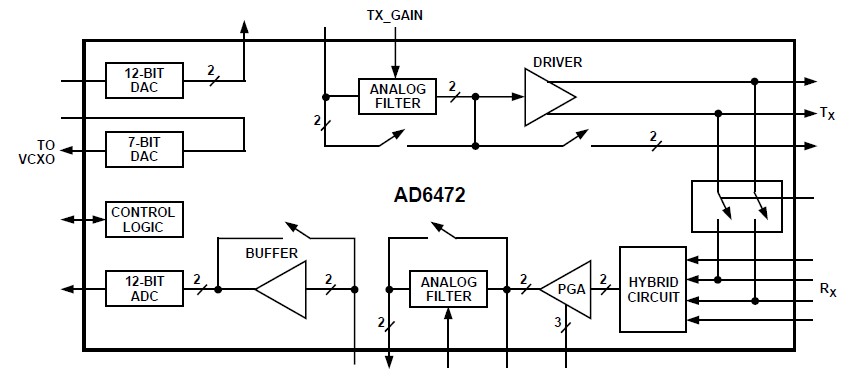

The AD6472BS is a single chip analog front end for two pair or single pair HDSL applications that use 1168 Kbps or 2.32 Mbps data rates. The AD6472BS integrates all the transmit and receive functional blocks together with the timing recovery DAC. The digital interface is designed to support industry standard digital transceivers. While providing the full analog front end for ETSI standards (two pair or single pair HDSL applications) the AD6472BS supports other applications because the architecture allows for bypassing the functional blocks.

Parametrics

AD6472BS absolute maximum ratings: (1)Supply Voltage: –0.3 V to +6.0 V; (2)Input Voltage: –0.5 V to VDD + 0.5 V; (3)Output Voltage Swing: –0.5 V to VDD + 0.5 V; (4)Operating Temperature Range (Ambient): –40℃ to +85℃; (5)Storage Temperature Range: –65℃ to +150℃; (6)Lead Temperature (5 sec) MQFP: +280℃.

Features

AD6472BS features: (1)Integrated Front End for Single Pair or Two Pair HDSL Systems; (2)Meets ETSI Specifications; (3)Supports 1168 Kbps and 2.32 Mbps; (4)Transmit and Receive Signal Path Functions; (5)Control and Ancillary Functions; (6)Single 5 V Power Supply; (7)Power Consumption: 320 mW—(Excluding Driver); (8)Package: 80-Lead MQFP; (9)Operating Temperature: –40℃ to +85℃.

Diagrams

|

AD640 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||||

|

AD640* |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||||

|

AD6402ARS |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||||

|

AD640JNZ |

|

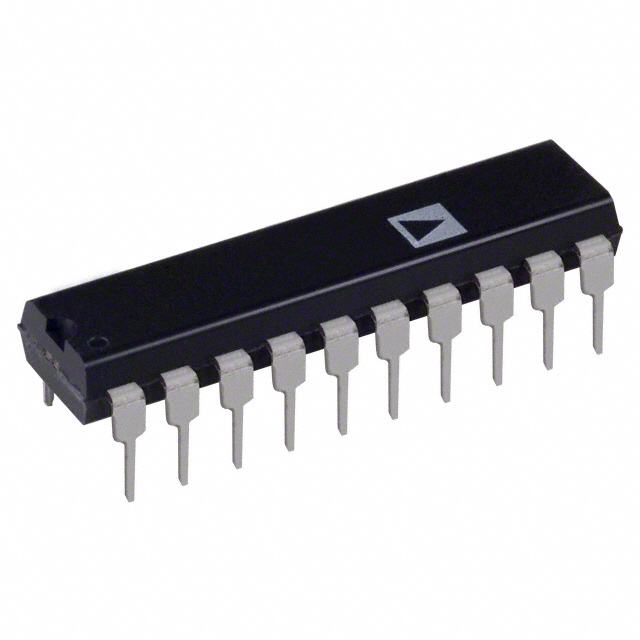

IC AMP LOG 2.3MA 20DIP |

Data Sheet |

|

|

||||||||||||||

|

AD640JP |

|

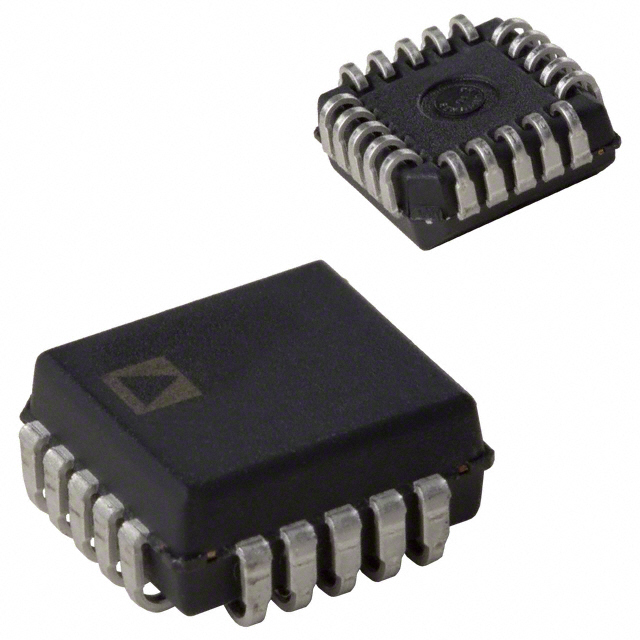

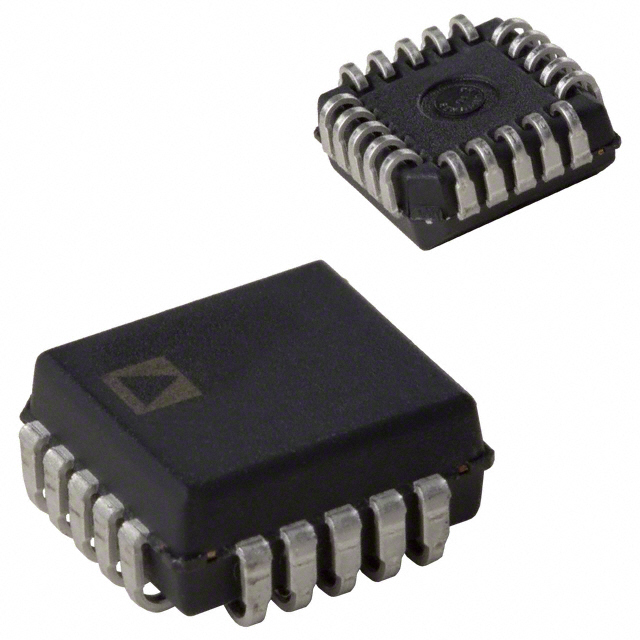

IC AMP LOG 2.3MA 20PLCC |

Data Sheet |

|

|

||||||||||||||

|

AD641APZ |

|

IC AMP LOG LP 2.3MA 20PLCC |

Data Sheet |

|

|

||||||||||||||

(China (Mainland))

(China (Mainland))